我们已经看到并联加法器电路使用级联组合完整的方案在这篇文章中并行加法器.同样在文章上平行减法器我们已经看到了两种设计n位并行减法器的方法。然而,从优化的角度来看,我们总是倾向于使用一个电路来完成多种操作。这意味着在我们的情况下,我们必须考虑是否有可能执行n位加法和n位减法使用一个数字电路,即a并行加法器或减法器电路。

答案是肯定的。这是因为,减法的过程二进制数就是它们2的补加法。

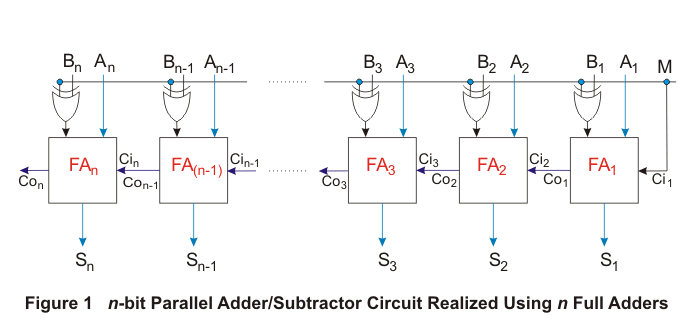

因此设计了并行加法器时的操作方式,从而提供了2的补在必要的情况下,可以作为并行加减器使用。控件完成的一个这样的设计XOR门如图1所示。

这里M线作为一条控制线,即根据M处提供的值,电路要么作为一个加法器,要么作为一个减法器。其原因如下所述。假设,如果m线被压低,那么每个异或门的一个输入将是逻辑0。这意味着在这种情况下,异或输出将是该数字的未改变二进制位

类似地,让我们现在分析M = 1的情况,意思是M控制线被拉高。在本例中,是每个的一个输入XOR门这是逻辑1。这意味着我们得到了位的补码

这表明二进制数在作为输入馈电给电路中的每个完整加法器之前进行补充。此外,对于相同的情况,甚至Ci1的第一个全加法器FA1在逻辑上是高的。因此,图1所示的全加法器级联排列有效地执行sn位二进制减法,其中二进制数

并行加法器或减法器的缺点

作为建筑并行加法器或减法器和a的很相似吗并行加法器(也对并行减法器),即使这种设计也容易受到纹波传播延迟的影响。然而,这类电路作为算术和逻辑(ALU)单元的一部分,在计算机领域得到了应用,有助于进行大量的计算。